產業觀察 | 深入剖析《集成芯片與芯粒技術白皮書》

前言

集成芯片與芯粒技術,作為持續推動摩爾定律發展、實現集成電路性能顯著提升的關鍵路徑,已日益顯現出其重要性和潛力。2023年10月,集成芯片前沿技術科學基礎專家組聯合中國計算機學會集成電路與容錯計算專業委員會,正式發布了《集成芯片與芯粒技術白皮書》。白皮書全面概述了集成芯片與芯粒技術,并揭示了其在集成電路領域的重要性和潛力。通過分析這些技術的原理、發展歷程和應用領域,展示了該領域前沿動態和未來的發展方向。

本文旨在全面而系統地闡述該白皮書的核心要點,討論集成芯片與芯粒技術的歷史演進路徑及未來可能的發展趨勢。

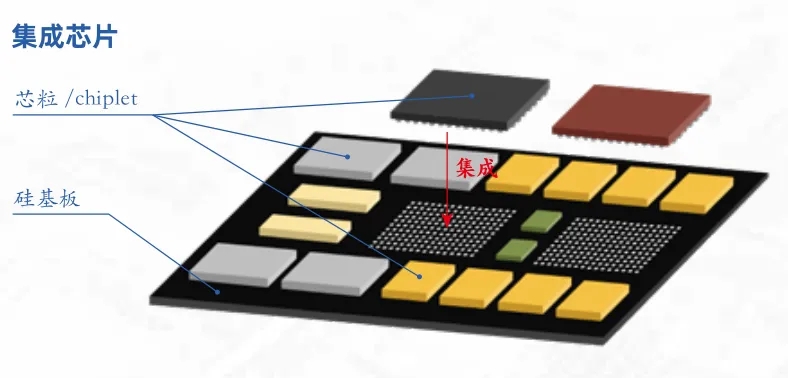

集成芯片與芯粒技術的定義

傳統集成電路是通過將大量晶體管集成制造在一個硅襯底的二維平面上形成的芯片。集成芯片是指先將晶體管集成制造為特定功能的芯粒(chiplet),再按照應用需求將芯粒通過半導體技術集成制造為芯片。其中,芯粒(Chiplet)是指預先制造好、具有特定功能、可組合集成的晶片(Die),也有稱為“小芯片”,其功能可包括通用處理器、存儲器、圖形處理器、加密引擎、網絡接口等 。

集成芯粒技術,作為一種先進的半導體技術,其核心在于將多個具備特定功能的芯粒進行整合,從而創造出一種集高性能與多功能性于一身的新型芯片集成方案。相較于傳統的集成電路技術,該技術成功地突破了單芯片制造在面積上的限制,進而實現了更高的集成密度與計算能力。

集成芯粒技術充分利用了芯粒的復用性與組合性,使得該技術能夠迅速響應并適應多樣化的應用需求。同時,通過引入敏捷制造的理念,該技術有效地解決了芯片個性化與通用性之間

此外,白皮書進一步指出:

“集成芯片采用系統工程學的原理,是集成電路性能提升的第三條路徑, 將引導集成電路設計的新范式。”

集成芯片設計對比傳統的集成電路單芯片設計,有如下優勢:

•更大的芯片尺寸,突破目前的制造面積局限,推動芯片集成度和算力持續提升;

•突破傳統封裝的互連帶寬、封裝瓶頸;

•芯粒級的IP 復用/芯粒預制組合,實現芯片的敏捷設計;

•更好地控制制造過程,減少制造缺陷率和成本;

•實現更多種類的新型芯片。

集成芯片的架構與電路設計

集成芯片領域迎來了一種革命性的設計新途徑,即自上而下的“分解-整合-集成”模式。在此模式下,無論是分解還是整合芯粒,都伴隨著復雜且精細的優化需求,這些需求遠遠超出了人工設計的處理能力,尤其是在面對龐大的解空間時。因此,白皮書深入剖析了在架構布局與電路設計層面所面臨的六項關鍵挑戰:

1.分解與組合難題

在芯粒分解過程中,必須全面考量成本、安全性及系統性能等多重約束條件下的優化問題。當前,芯粒分解方案多依賴于設計人員的經驗,這種手工分解方式難以全面覆蓋所有潛在的設計空間,因而往往難以達到最優的效益與成本平衡。同樣,在當前的芯粒組合實踐中,設計人員需基于用戶的具體需求與優化目標,從龐大的芯粒庫中仔細篩選并搭配出最優的芯粒組合方案。然而,這一過程往往依賴于手動設計,導致集成效率低下,且難以實現深度的優化效果。因此,自動化芯粒組合技術的研究與發展顯得尤為重要。

2.芯粒間互連網絡

白皮書指出,在片上網絡與基板網絡的設計架構中,存在三項至關重要的核心技術,即互連拓撲、路由策略以及容錯機制。當前,互連拓撲領域正面臨一個顯著挑戰,即通用性與性能之間的平衡問題。在集成芯片的設計中,路由算法的設計必須兼顧多個核心特性,包括拓撲無關性、完全可達性、故障獨立性和可擴展性。為了優化系統的容錯效能,可以采用能夠容忍故障并提供冗余路徑的結構布局方式。

3.多芯粒系統的存儲架構

在集成芯片系統中,多芯粒的存儲架構作為核心組件,對提升訪存效能及降低功耗具有顯著影響。此架構與傳統眾核或服務器芯片的存儲設計存在諸多共通之處,其核心優化目標聚焦于增強訪存效率與縮減目錄管理等額外成本。據此,多芯粒系統的存儲架構優化策略聚焦于兩個核心維度:一是多級存儲結構的精細組織與配置,二是存儲管理的優化與革新。白皮書明確指出,存儲結構的組織模式正經歷從傳統平面架構向更為高效的垂直架構轉型的深刻變革。

4.芯粒互連的接口協議

面向芯粒的接口協議主要分為物理層接口協議與完整的協議棧兩大類別。其中,多數物理層接口協議或標準聚焦于引腳定義、電氣特性、bump map等基礎性特征,旨在確保數據比特流能夠實現點對點傳輸。協議棧則進一步細化了路由策略、數據結構、可靠傳輸機制、一致性要求以及流量控制等方面的規范,從而能夠構建出端到端的可靠數據傳輸體系。芯粒互聯協議應當實現與廠商、架構以及制造工藝的解耦,以確保其具備廣泛的兼容性和高度的開放性。這一特性對于滿足芯粒異構互聯以及跨廠商互聯的實際需求至關重要。

5.芯粒間的高速接口電路

芯粒間的高速接口電路涵蓋了幾類:一是專為2.5D/3D集成工藝設計的有線(Wireline)并行通信接口;二是基于電感耦合原理的無線互連通信接口;三是實現高帶寬傳輸的光電互連接口。據相關白皮書闡述,當前高速接口電路領域仍面臨一系列亟需突破的關鍵挑戰,包括但不限于開發能夠克服功耗瓶頸的新型電路、研制能夠兼容不同信道的可重構收發機、建立自適應的檢測與校正機制,以及實現接口電路跨工藝自動化遷移的技術方案等。

6.集成芯片大功率供電電路

當前,單顆高性能芯片的功耗普遍位于百瓦級別,具體實例包括Intel第13代CPU的PL2 TDP高達219W,以及NVIDIA H100 GPU的TDP達到350W。展望未來,當集成芯片擴展至百芯粒規模時,其供電需求將急劇增加至數千瓦乃至萬瓦級別。針對此,集成芯片的大功率供電需求迫切要求我們在多級供電架構、電源分配網絡以及無源器件集成等多個關鍵領域進行深入研究。這些研究旨在確保集成芯片的供電穩定性,同時提升供電效率,并進一步減小供電系統的整體體積。

集成芯片EDA和多物理仿真

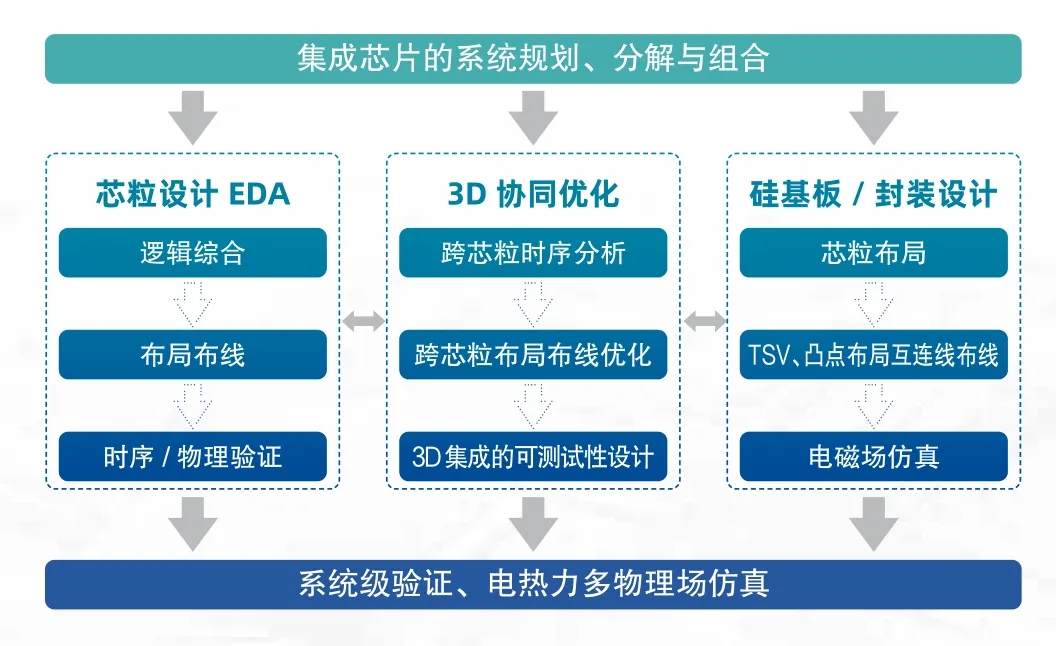

集成芯片對自動化設計方法與EDA工具的新需求

集成芯片的規模顯著超出常規單芯片,鑒于此,針對集成芯片的設計工作,需要更多的功能的自動化設計EDA 工具,包括:

•集成芯片的系統規劃與分解組合

•芯粒設計

•硅基板(Interposer)和封裝設計

•3D 協同優化設計

•系統級驗證與多物理場仿真

集成芯片的自動化設計方法與 EDA 工具

芯粒間互連線的電磁場仿真與版圖自動化

隨著芯粒數量和種類的顯著增長,芯粒之間的互連線數量也急劇攀升。由于片上布線與芯粒間布線在基礎電學約束方面存在顯著差異,因此,現有的針對片上布線的EDA工具在應用于集成芯片的片間布線時面臨挑戰。2.5D/3D集成工藝中引入的微凸點和TSV結構,其復雜的寄生效應對信號的影響難以通過傳統的RLC集總電路模型進行精確評估。

白皮書中認為:

增強電場積分方程方法是一種針對分層互連線結構進行電磁仿真的有效方法。相比有限元,計算速度慢,消耗資源多,需要對整個空間進行網格劃分,不適合求解開放空間和時變問題。

芯粒尺度的電—熱—力多場耦合仿真

隨著電路特征尺寸的持續縮減以及封裝系統復雜性的顯著提升,(例如集成芯片)技術的快速發展,封裝設計領域正面臨前所未有的挑戰,必須解決在高頻、高功率及應力變化等條件下的電磁分布效應、熱效應及力學效應問題。鑒于特征尺寸的縮減與功率的增強,溫度呈現顯著上升趨勢,尤其是在熱點區域,此現象將不可避免地削弱電子封裝的性能及縮短其使用壽命,并可能因電遷移作用而引發金屬化失效。此外,大幅的溫度梯度與不匹配的熱膨脹系數將催生誘導熱應力,此類應力有可能引發芯粒的機械故障,具體表現為分層、剝離等現象。鑒于此,需要一種集成了電-熱-力多物理場耦合技術的計算機輔助設計方法,以全面且同步地應對電氣與熱管理方面的挑戰。

集成芯片的可測性和測試

集成芯片的可測性和測試技術在提升制造良率、精確定位缺陷位置及增強集成芯片可靠性方面扮演著核心角色。因此,深入探究一系列關鍵技術,如最大公約芯粒測試集的構建、互連線冗余設計的優化、協議修復機制的完善、可測試性結構的精心設計、全生命周期管理的實施以及有源硅基板測試的精確執行等,顯得尤為重要。這些技術的應用,旨在實現缺陷的快速識別、高效替換或修復,進而顯著提升集成芯片的制造良率,并有效壓縮制造成本。

集成芯片特色制造工藝

RDL/硅基板(INTERPOSER)制造工藝

相較于傳統的封裝基板(Substrate)級 2D 互聯技術,集成芯片工藝融入了銅互連等先進的芯片制造技術,從而催生出了具備新型形態與功能特性的芯粒。其中,最具代表性的元素即為2.5D集成技術中的硅基板(Interposer)。硅基板通過微凸點(Micro-bump)和C4凸點(C4 bump)與上層的芯粒以及底層的封裝基板實現電信號的連接。在2.5D集成芯片中,硅基板的面積直接決定了整個集成芯片的面積。

•單芯片制造的最大面積上限由光刻機的光罩尺寸(reticle)決定,如何實現超過3-4個光罩尺寸的硅基板是一項重要的課題

•TSV的深度一般小于硅片的厚度,因此需要將硅基板減薄到100微米以下,大面積硅基板易發生翹曲,甚至斷裂

•多次曝光/拼接縫合(stiching)技術、高密度高深寬比的TSV工藝也是硅基板制造中的難題

高密度凸點鍵合和集成工藝

在集成芯片領域內,互連密度已經實現了從傳統百微米級節距向微米級節距的顯著提升,并且正迅速向更為精細的亞微米級節距邁進。鑒于大規模芯粒及其封裝結構所呈現的高度復雜性、高密度互連特性及超高密度鍵合要求,其封裝設計過程中的缺陷預測與抑制面臨顯著挑戰。因此,深入研究并發展高密度、高可靠性的凸點鍵合及集成工藝顯得尤為迫切。在三維空間內,芯片 / 芯粒間互連可分為三類:

•芯粒表面與外界的垂直互連通道,包括傳統的凸點、微凸點和新興的混合鍵合互連界面,已逼近10微米的物理極限

•芯粒間水平互連導線,主要指基板或重布線層的導線陣列,向亞微米級節距進行快速微縮

•芯粒內部的垂直通孔結構,即硅通孔,主要實現多層芯粒堆疊中的互連

白皮書認為,混合鍵合可有效突破 10微米極限,向亞微米級節距進行快速微縮。與凸點鍵合相比,混合鍵合具有結構、材料上根本的革新,并帶來顯著的性能優勢:

•采用內嵌式超平表面銅接口,避免了鍵合對準過程中接口倒塌變形、鍵合空洞及相應失效風險;

•采用預填充式無機介電層,相比于傳統有機底填料,顯著提高了熱穩定性

但同時,混合鍵合面臨的挑戰包括:

•從當前芯片后道工藝(BEoL)大馬士革工藝出發,制造適合混合鍵合的頂部金屬-介電層,保證高鍵合強度

•開發面向混合鍵合的高精度高潔凈度劃片技術,保證鍵合前后芯片邊緣無崩邊、隱裂

•控制晶圓整體翹曲和表面平整度,實現整片晶圓或芯片的無空洞完整鍵合

基于半導體精密制造的散熱工藝

芯片熱管理技術的發展歷程可以劃分為以下三個關鍵階段:逐層散熱的方法(可達 200)、芯片→熱沉→組件殼體散熱( 可達500)、近結點冷卻技術( 可達1000)。后兩類散熱工藝,需要全面考量材料的導熱效能、熱膨脹行為、電學性能以及加工制造工藝的可行性,以確保流-固-熱-力-電之間的兼容性。鑒于芯片內部元件繁多且材料特性各異,常常還需在芯片層面集成微閥、連接管道等組件,這進一步加劇了三維堆疊芯片內部流體與電學連接的復雜性。因此,當前亟需攻克的技術難點包括:近結點微通道設計的優化與強化換熱策略、多層異質界面封裝集成技術,以及芯粒集成芯片在熱-電-力-流協同設計技術。

集成芯片面臨的挑戰與機遇

最后,白皮書總結了集成芯片目前面臨的三大科學問題與十大技術難題:

三大科學問題

•芯粒的數學描述和組合優化理論

•大規模芯粒并行架構和設計自動化

•芯粒尺度的熱力電多場耦合機制與界面理論

十大技術難題

•芯粒的抽象描述問題

•復雜功能需求分解映射到大規模芯粒的問題

•多芯并行體系結構和互連接口

•萬億晶體管芯片的仿真問題

•芯粒的測試和容錯問題

•萬瓦功耗芯片散熱和供電問題

•大尺寸有源/無源硅基板的架構設計與制造問題

•高速高密度連線的信號完整性問題

•芯粒級熱-力-電耦合仿真和工具

•大尺寸芯片的翹曲問題